ich brauch nen Plan. Dampfbügeleisen (Schwester)

Dampfbügeleisen: Aus Platine einen Schaltplan erzeugen.

|

|

|

|

|

|

|

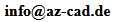

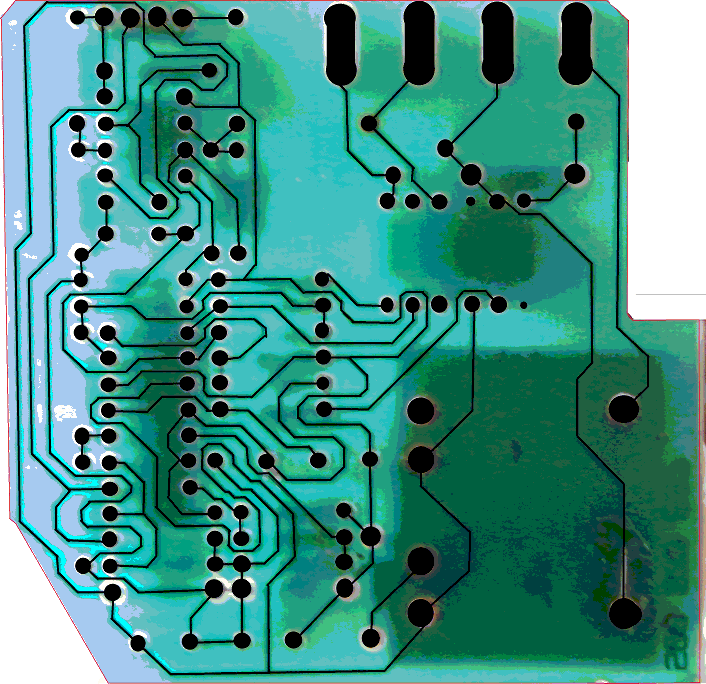

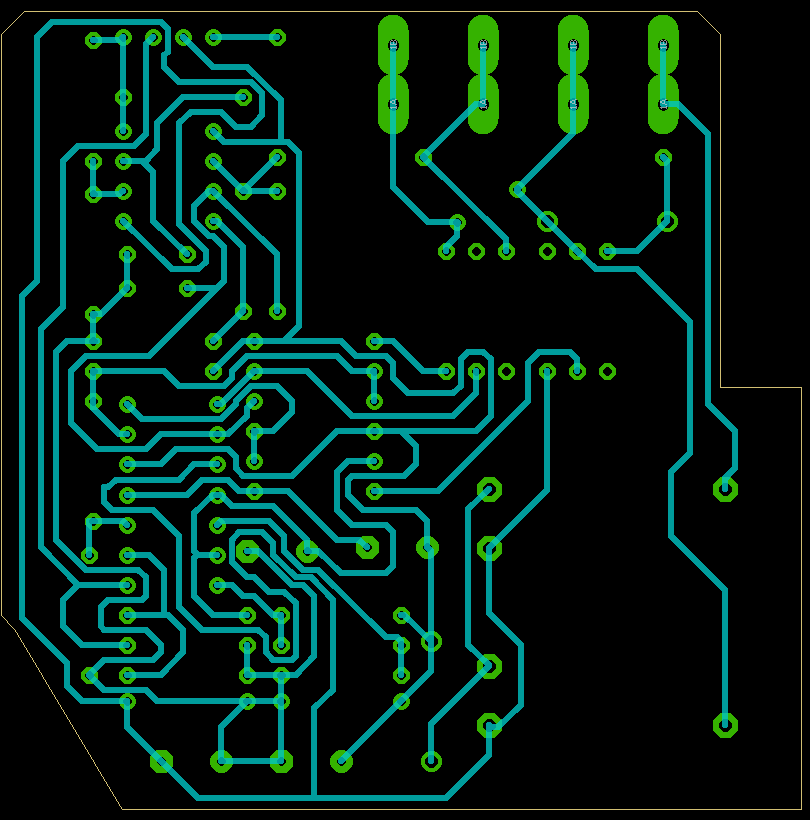

Leiterplatte von oben. Foto möglichst verzerrungsfrei. |

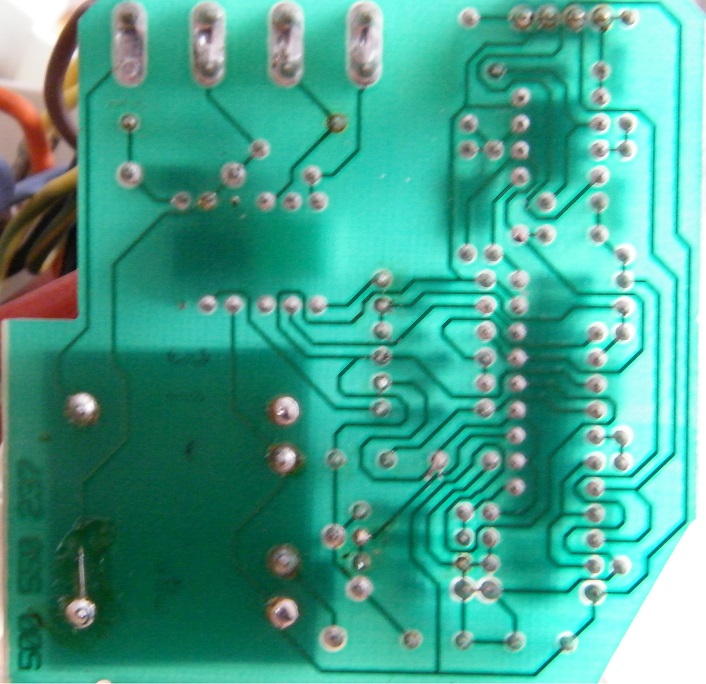

Foto der Lötseite möglichst verzerrungsfrei. |

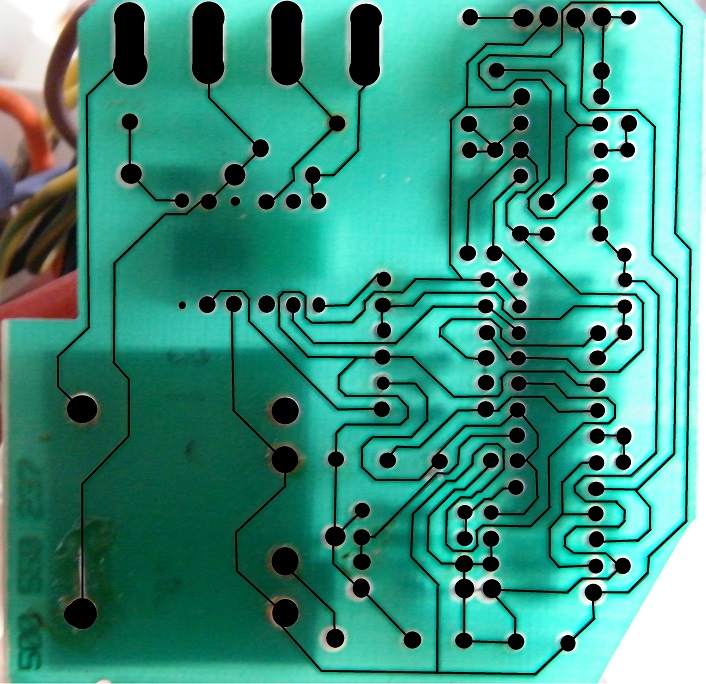

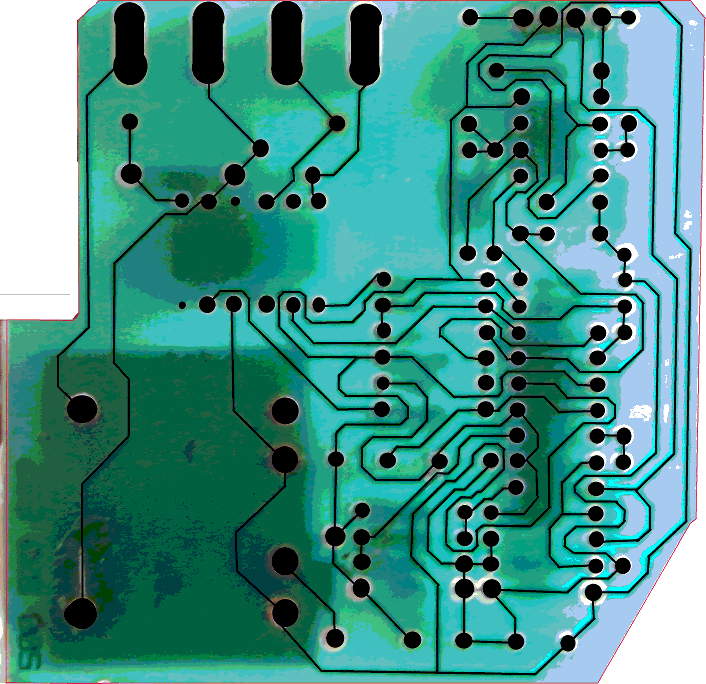

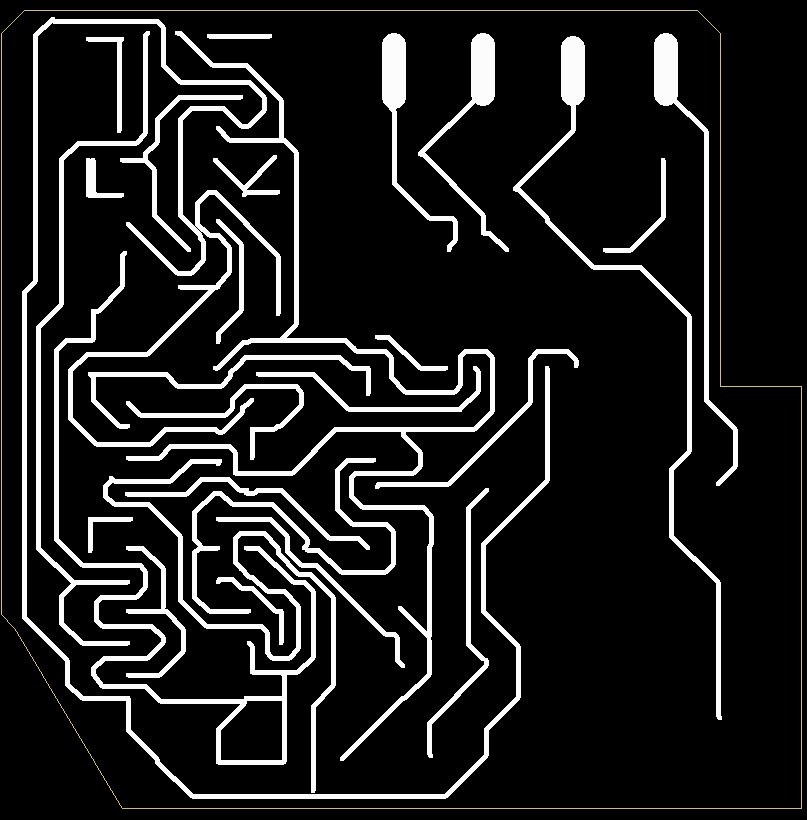

Als Hilfsmittel, wenn der Kontrast der Leiterbahnen unter dem Lötstoplack zu gering ist. Die Kupferbahnen mit einer eindeutigen Farbe (hier schwarz) als Linien nach- zeichnen. Dann reicht es, wenn im Menü des RUN import-bmp.ulp die Farbe schwarz zum importieren selektiert wird. Bei vielen Schattierungen der Farben, wird es etwas Mühselig die richtigen Farben zu markieren, die die Leiterbahnen darstellen. |

Dann die Farben auf 256 (evtl. gleich auf 16) reduzieren. Dazu mit speichern unter ... 16-Farben Bitmap 256-Farben Bitmap |

und dann noch das Bild spiegeln, dann wir routen ja die Platine von oben, also von der Bauteilseite. Das Foto ist ja von der Rückseite und muss deshalb gespiegelt werden, damit es wieder zur Bestückungsseite Deckungsgleich ist. |

Die Bitmap-Datei in Paint entsprechend so weit zuschneiden, dass die Ränder der Platine auch am Rand des Bildes enden.

Die Bitmap-Datei kann jetzt mit RUN import-bmp.ulp eingelesen werde.

Hier auf die Skalierung achten.

In Paint sieht man am unteren Rand des Programmfenster die Größe der Datei in Pixel. Beite Höhe.

Im Dialogmenü des ULP stellt man auf bei Format "Aspect/Ratio", bei Unit mm, sofern man die Platine in mm gemessen hat.

Bei Value between 0.0001 und 2000.0mm gibt man die gemessen Breite der Plaitne ein.

Das ULP berechnet anhand der Bildbreite (Pixel) und der angegebenen realen Breite in mm den Skalierungsfaktor.

Die 200 für den Layer der zu importierenden Farbe (Pixel) kann man stehen lassen.

Jetzt noch [ OK ] drücken und das ULP erzeugt ein Script das anschließend automatisch eingelesen wird.

Man kann sofort die Vorlage der Leiterbahnen erkennen.

|

|

|

|

|

|

|

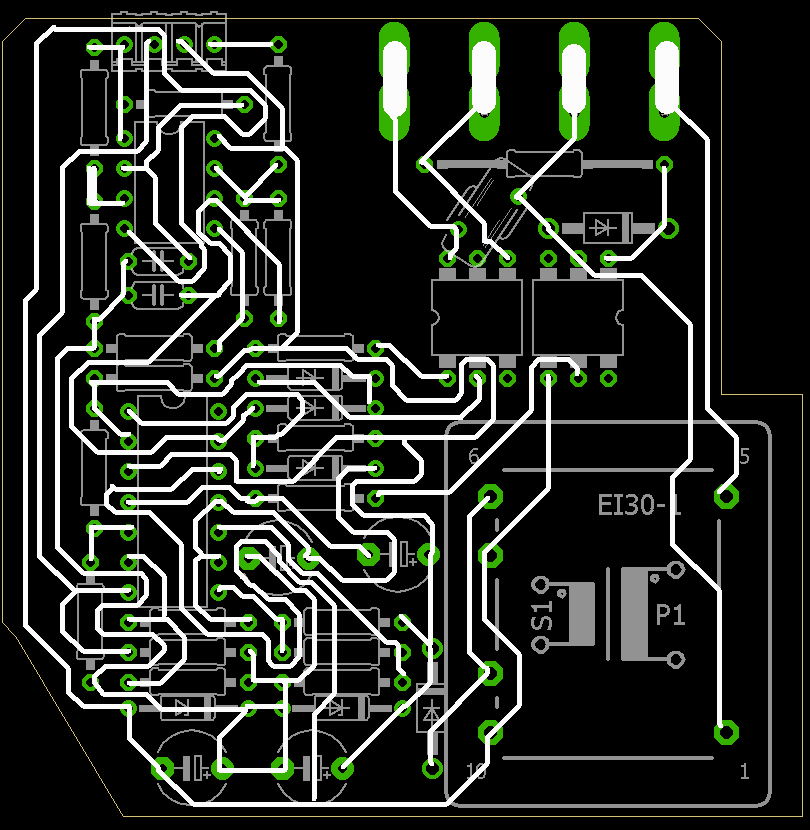

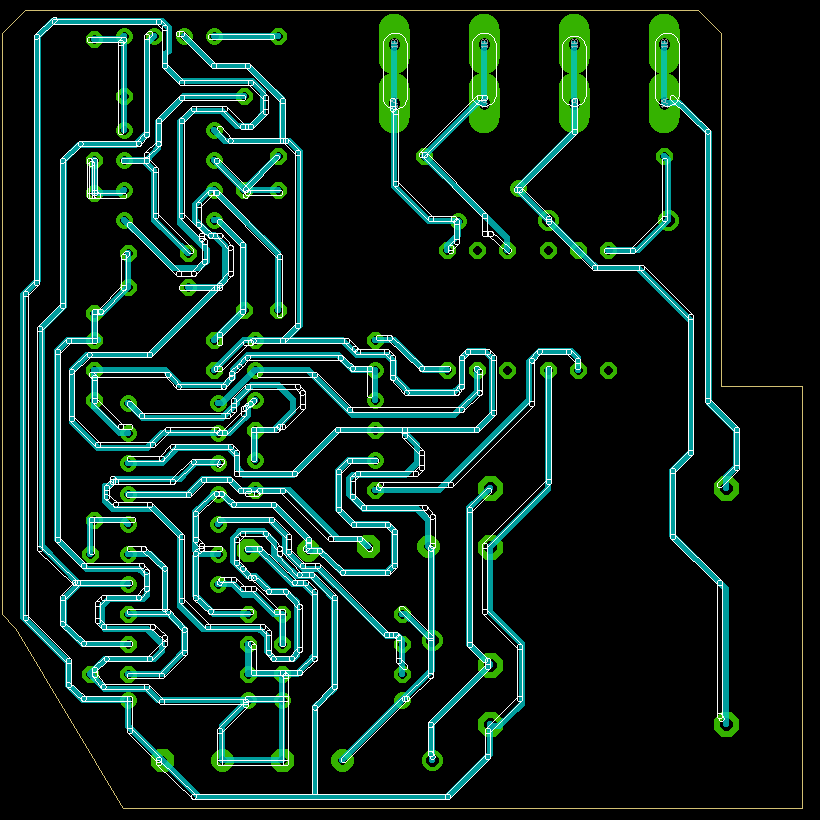

Nach dem Import der BMP-Datei hat man die "Leiterbahnen" als Vorlage. |

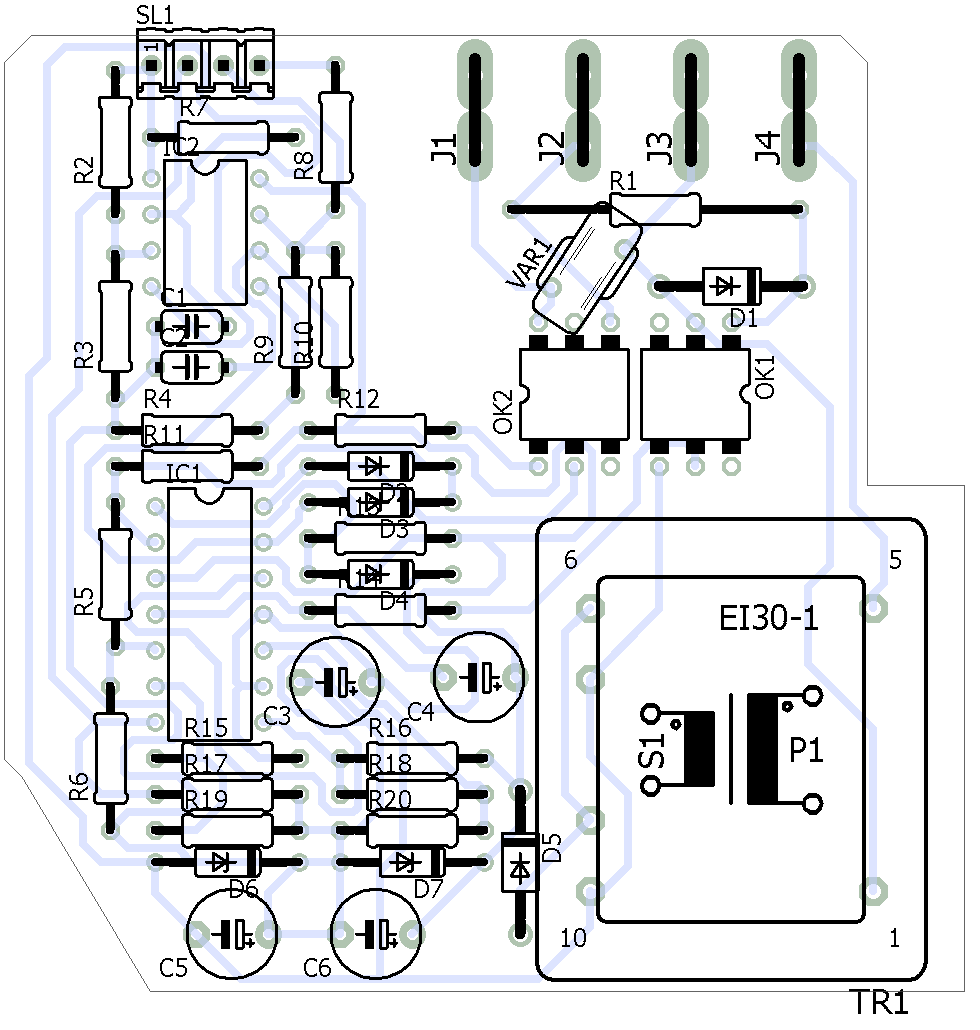

Jetzt die Packages platzieren, so das an den Enden und Verdickungen der Leiterbahnen die PADs des jeweiligen Package liegen. Als Vorlage dazu dient das Foto der Oberseite.

Hier kommt es darauf an,

Ist später für das |

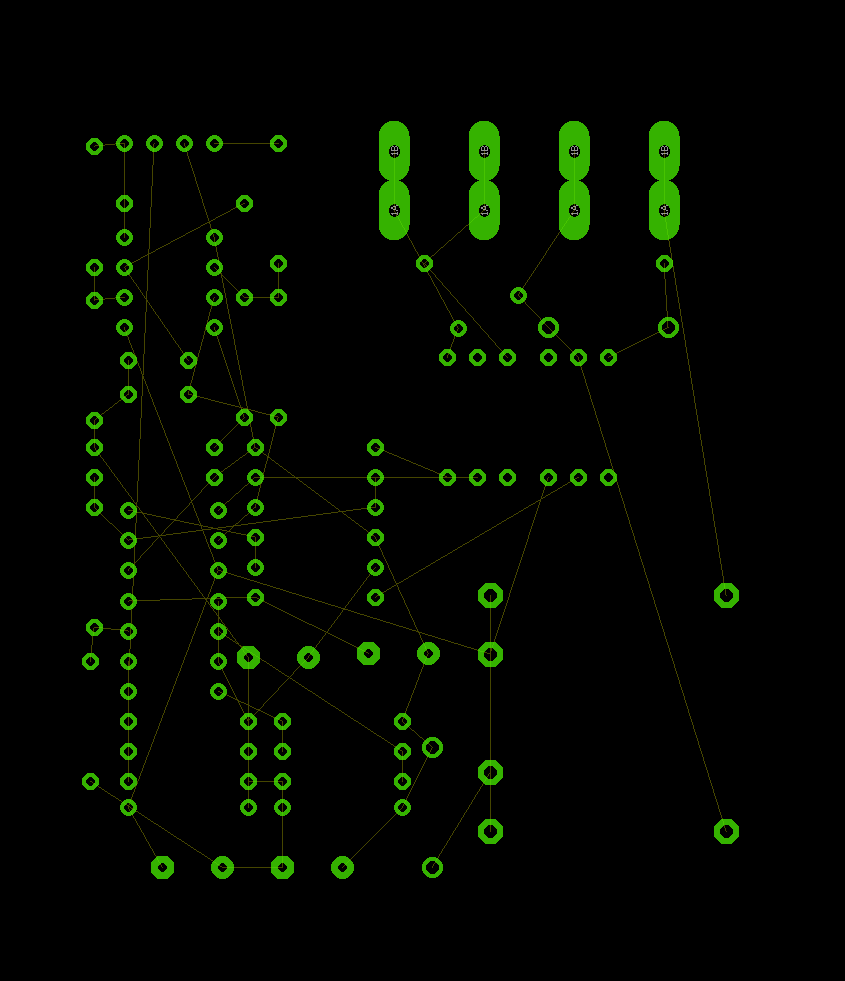

Mit SIGNAL die PADs die an den Enden bzw. Verdickungen unter der Leiterbahnvorlage liegen verbinden. Das erzeugt zuerst mal sogenannte Luftlinien. |

Schaltet man alle Layer bis auf PADs (17) und unroutet (19) aus, dann sieht das Ergebnis so aus. |

Jetzt schaltet man für den Layer der Referenz ein entsprechendes Füllmuster ein, so dass man beim ROUTEn die Leiterbahn die jetzt am Cursor hängt, durch die Vorlage hindurch sehen kann. Nun mit entsprechendem Knickmodus die Vorlage abrouten, bis man am nächsten PAD ankommt.

Hier unterbricht EAGLE

Jetzt auf die linke Maustaste

Diesen Vorgang so lange |

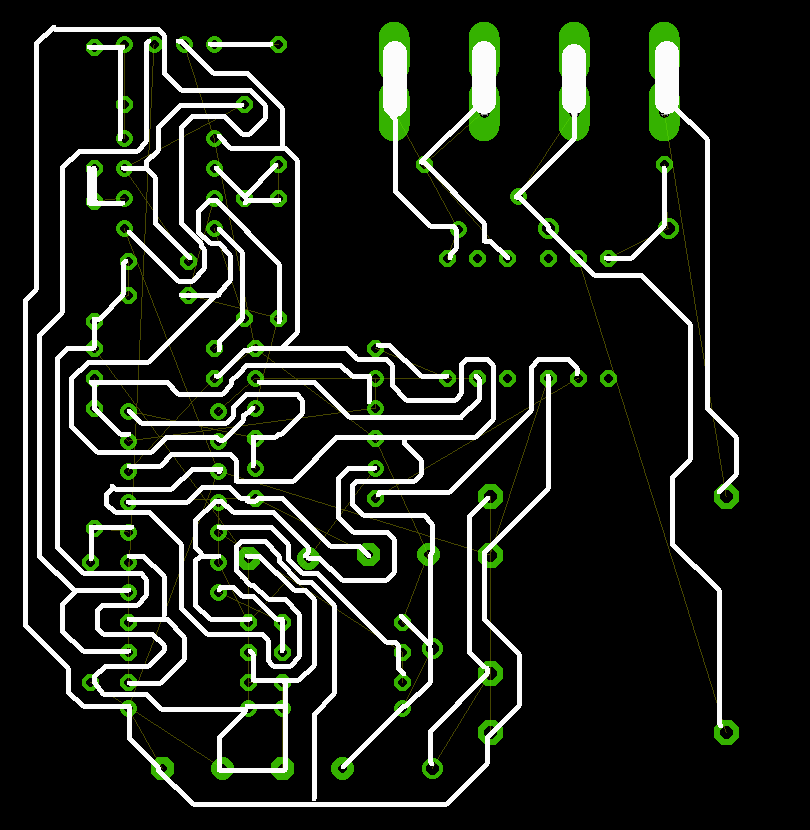

Den Vorlagen-Layer wieder ausschalten und man sieht das geroutete Ergebnis. Zum Schluss nochmal RATSNEST ausführen, hier sollte EAGLE Nichts zu tun! melden. Ansonsten wird die Anzahl der Luftlinien angezeigt. Dann muß man nochmal mit ROUTE ran. |

Die Layer entsprechend einschalten, so daß man die gewünschte Ansicht hat.

Jetzt geht es ans Eingemachte.

1. Der Schaltplan muß konsistent zum Layout angelegt werden.

Dazu gibt man im Board die Stückliste aus, mit der Information des Packagenamen und der Bibliothek.

vIm Schaltplan holt man sich jetzt Stück für Stück die Bauteile der entsprechenden Packages.

Hier ist die Kunst, anhand des Package und der Bibliothek zu erkennen, ob es sich um einen Widerstand, Kondensator,

Spule, Diode, Transistor, IC ... handelt.

Die Position im Schaltplan ist jetzt erst mal egal, hauptsache die Symbole sind aus dem gleichen Device und

der Bibliothek wie die Packages im Board.

1a Dann sieht das so aus. Nur die Bauteile platziert.

2. Jetzt noch die VALUE angeben, das ist das dritte Kriterium für die Konsistenz.

3. Im Layout erzeugt man mit RUN import-netlist2sch.ulp eine Verbindungsliste der gerouteten Signale.

Das ULP erzeugt ein SCRIPT dass am Ende zum Schaltplan wechselt und sich selbst import-netlist2sch.ulp erneut startet.

Hier ermittelt das ULP die PINs der Symbole anhand der CONNECTion zu den PADs im Device, und zeichnet mit NET

die Netze im Schaltplan ein.

Hier nicht erschrecken, die Netzlinien laufen u.U. etwas "schräg". Soll heißen, die Verbindungen der PINs sind exakt

die Verbindungen der PADs im Layout, nur optisch anders.

3a Das sieht dann so aus. Die NET-Wire wie Gummibänder.

Der Grund ist ganz einfach. Im Package (bei ICs) werden die PADs an einer Ecke oder Mitte einer Seite mit 1 beginnend gegen den

Uhrzeigersinn gezählt. Das Symbol(e) zeichnet man i.d.R. so, dass man es versteht.

Weitere Erklärung gibt es im Quelltext des ULP.

Einfaches Beispiel: 4-fach NAND-Gatter 7400. 14 Beinchen zu 7 links und 7 rechts am Gehäuse.

Das Symbol besteht hier aber aus 5 Symbolen, nämlich 4 Gatter zu je 3 Pins (ich liebe die alte Symbolik mit den Halbsemmeln)

und einem Symbol mit 2 Pins für die Stromversorgung. Und hier kommt auch schon ein Extrem. Das Package ist wie es ist (Physikalisch),

aber die 5 Gates im Schaltplan, kann ich an jeder beliebigen Position platzieren, sogar auf unterschiedlichen Schaltplanseiten.

Und deshalb sieht der Schaltplan erst mal verrückt aus.

Jetzt ein WICHTIGER Punkt.

4. Den Schaltplan und das Board Konsistent machen!

Dazu benutzt man den ERC.

Der ERC prüft jetzt ob die Bauteil-NAME (PART im SCH und ELEMENT im BRD) identisch ist.

Hier kommt u.U. schon der erste Konsistenz-Fehler.

Dann wird überprüft ob der VALUE identisch ist.

Als nächstes ob das Package jedes Bauteil im Layout aus der gleichen LBR wie das Device (Sybmol) im Schaltplan stammt.

Dann ob die PAD-Namen des Package im Board den gleichen Namen wie die hinterlegten PAD-Namen im Device besitzen.

Anhand der CONNECT-Liste im Device (PIN - PAD) wird jetzt überprüft ob die SIGNAL-Namen mit den NET-Namen

überein stimmten.

Ist das der FAll, hat man ein konsistentes Paar SCH/BRD.

EAGLE meldet dann Board und Schaltplan sind konsistent, und zeigt an der rechten unteren Ecke von SCH/BRD

einen grünen Punkt.

Jetzt kommt die Kür für den Anwender.

5. Mit MOVE, ROTATE, MIRROR die Symbole so anordnen, dass möglichst direkte Verbindungen entstehen.

Hier hilft vor allem SPLIT in Verbindung mit MOVE um die Netze anschaulich zu verlegen.

Ganz Wichtig: Hier nie DELETE benutzen [1], denn sonst wird ein Netz aufgetrennt

und der kleinere Teil bekommt einen "erzeugten"* Namen.

* Von EAGLE erzeugte NETz-Namen erkennt man an N$ am Anfang des Namen.

[1] Je nachdem wo man ein WIRE-Segment das NET gelöscht hat, wird im Board auch die Leiterbahn teilweise gelöscht.

Die Konsistenz geht hier nicht verloren, weil EAGLE dafür sorgt dass die richtigen Teile gleich benannt werden.

Aber das Layout wird in sofern zerstört, dass Teile des Kupfer verschwinden, und dadurch die Platine nicht mehr

funktionieren wird!

Am Ende soll ja ein Schaltplan entstehen, der bezogen auf den Strom/Signalfluss lesbar ist.

Bei komplexen Schaltungen ist das nicht immer so Einfach, da es Verzweigungen und Rückkoppelwege gibt.

Beispiel: Operationsverstärker. Hier gibt es zu 99,9% eine Rückkopplung vom Ausgang zu einem der Eingänge.

Und hier ist eben der Anwender gefragt wie die Bauteile und NETze positioniert werden, dass es auch Übersichtlich ist.

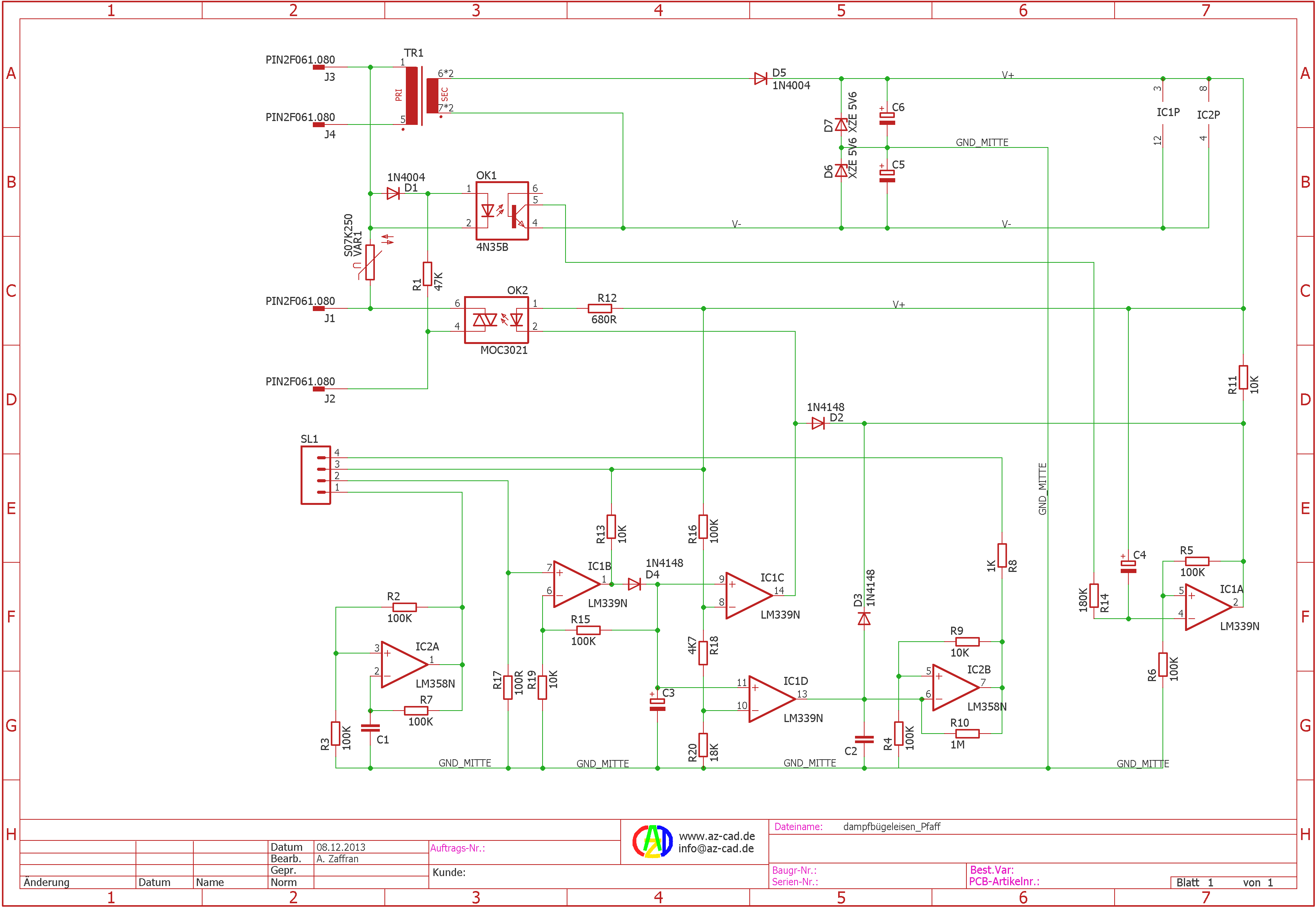

Hier der Schaltplan nach entsprechender Nacharbeitung.

Damit kann man arbeiten.