# EAGLE - CAD Schulung

## EAGLE ERC/DRC

### Electrical-Rule-Check / Design-Rule-Check

Seite 001: Inhaltsverzeichnis

Seite 002: Electrical Rule Check

Seite 003: ERC-Fehlermeldungen 1

Seite 004: ERC-Fehlermeldungen 2

Seite 005: ERC-Fehlermeldungen 3

Seite 006: ERC-Fehlermeldungen 4

Seite 007: Design-Rule-Check POLYGON

Seite 008: DRC-Fehlermeldungen 1

Seite 009: weitere Dokumentationen

Seite 010: Ende der Dokumentation DRC/ERC

Für die Erstellung des INDEX in diesem Schaltplan unbedingt die folgende Option des ULP benutzen:

RUN e-seiten-index EAGLE-Schulung\_AZ-CAD

## Electrical-Rule-Check

A

Um zu überprüfen ob der Schaltplan korrekt verdrahtet ist, startet man mit ERC den Electrical Rule Check.

In der Regel sind die Kontaktpunkte von PINs mit einem NET verbunden, was der ERC überprüft und entsprechend der Pin-Direction mit einer Meldung reagiert.

Um Netze zu zeichnen benutzt man den NET-Befehl, da er im Gegensatz zum WIRE-Befehl in den NET-Layer schaltet, am Kontakt des Pin zuverlässig kontaktiert und bei Abzweigungen einen Junction (Verbindungspunkt)\*<sup>[1]</sup> setzt, als optische Anzeige einer elektrischen Verbindung.

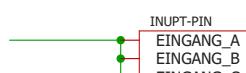

Zusätzlich öffnet der NET-Befehl ein Menü wenn ein BUS selektiert (angeklickt) wurde und bietet die in dem BUS verfügbaren NETze als Auswahl an.

Allerdings kommt es öfters vor, das Anwender nicht den NET-Befehl, sondern den WIRE-Befehl benutzen, oder sogar mit MOVE und COPY ein NET zeichnen, was dann zu entsprechenden Fehlermeldungen des ERC führt.

Ein mit MOVE auf einen Kontakt eines PIN gezogener NET-Wire verbindet das NET nicht mit dem PIN, ebenso ein NET-Segment das mit COPY auf einen PIN gesetzt wird. Hier handelt es sich lediglich um eine optische Überlappung, nicht aber um einen elektrischen Anschluß

Im Gegensatz zu MOVE Netwire, erzeugt ein MOVE Symbol (Bauteilsymbol) eine Kontaktierung der Pins mit dem entsprechenden NET-Wire.

Wird ein Symbol abgesetzt, egal ob mit ADD, MOVE, ROTATE, MIRROR, COPY, dann überprüft Eagle ob an den Koordinaten der jeweiligen PIN-Kontaktpunkte ein NET gezeichnet ist. Sitzt der NET-Wire exakt auf der Koordinate den PIN-Kontaktpunkt, dann wird das NET mit diesem PIN "elektrisch" angeschlossen. Trifft der PIN-Kontaktpunkt auf ein Ende des NET-Wire wird nur angeschlossen, innerhalb des NET-Wire wird gesplittet und ein Junction gesetzt. Treffen an der abgesetzten PIN-Koordinate zwei Wireenden zusammen wird auch ein Junction gesetzt. \*[1]

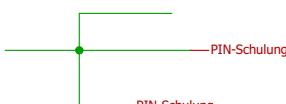

PIN-Schaltung

Trifft der PIN-Kontaktpunkt auf des Ende des NET-Wire wird nur angeschlossen, trifft der PIN-Kontaktpunkt innerhalb der Linie (zwischen den beiden NET-Wire-Endpunkten), dann wird das NET angeschlossen und zusätzlich das Wire-Segment gesplittet und ein Junction gesetzt.

PIN-Schaltung

\* [1]

## ERC - Fehlermeldungen

Findet der ERC ein NET-Wire das nergends angeschlossen ist, wird im ERC-Fehler-Menü folgende Meldung eingetragen:

- Keine Pins an Netz xxx

PIN-Schaltung

Findet der ERC ein NET-Wire das an einer Seite nicht angeschlossen ist, wird im ERC-Fehler-Menü folgende Meldung eingetragen:

- Nur ein Pin an Netz xxx

PIN-Schaltung

Findet der ERC ein NET an dem mindestens zwei PINs angeschlossen sind, so wird an den eventuell weiteren offenen NET-Wire-Enden keine Fehlermeldung erzeugt

Um offene NET-Wire zu finden, benutzt man RUN extended-erc.ulp

G

## ERC - Fehlermeldungen

A

Findet der ERC ein NET-Wire das optisch auf einen PIN liegt, aber elektrisch nicht angeschlossen ist, wir folgende Fehlermeldung ausgegeben:

### - Nicht angeschlossener Pin

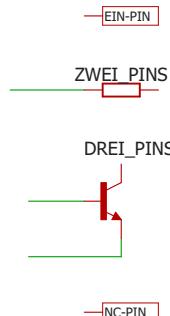

Bei Symbolen mit nur einem Pin muß der Pin an einem Netz angeschlossen sein.

Bei Symbolen mit zwei Pins muß ebenfalls jeder Pin an einem Netz angeschlossen sein, da sonst kein geschlossener Stromkreis entstehen kann.

Ab drei Pins in einem Symbol müssen nur 2 Pins angeschlossen sein um einen geschlossenen Stromkreis zu bilden. Eine genauere Analyse der Funktionen der Pins ist nicht integriert.

So kann z.B. von einem Transistorsymbol für bestimmte Zwecke nur eine Diodenstrecke benutzt werden, ohne dass der ERC eine Fehlermeldung erzeugt.

Weitere Infos zu nicht angeschlossene Pins siehe im Absatz :

### \* Nicht angeschlossener INPUT-Pin Partname Pinname

C

### - NETZ überlappt Pin

1. keine NET-Linien über den roten Teil des PIN zeichnen nur eine Seite (grüner Kreis im Pins-Layer) ist der Kontaktpunkt.

2. Fallstrick in der LBR - SYMBOL

Wenn zwei Pins mit entsprechender Länge (Length) im Symbol so platziert sind, daß das Ende des Pin auf den Kontaktpunkt des anderen Pin zum liegen kommt muß die Länge im Symbol entsprechend geändert werden oder die Pins weiter auseinander platziert werden.

-- Lösung: dafür gibt es das check-erc-net-beruehrt-pin.ulp

-

ERCCHECK1

N\$10 N\$12

N\$11 N\$13

Die Linien überlappen und die Kontaktpunkte mit den Enden der Linien überschneiden sich.

ERC-Fehler Netz überlappt PIN

### - NETZ überlappt Pin

1. Hier wurde ein NET quer bzw. teilweise zurück über einen PIN gezeichnet

E

### - Pins überlappen

Hier wurden die Symbole so nah aneinander platziert, dass sich die Pins überlappen, so dass sich die Kontaktpunkte im anderen Symbol befinden.

Schalte mit DISPLAY den Pins-Layer 93 ein, um die Kontaktpunkte (Kreise) und die Direction so wie den Addlevel der Pins zu sehen.

### - Segment des Netzes .... hat keine erkennbare Verbindung (z.B. Label, Bus oder Supply-Pin) zu anderen Segmenten des selben Netzes

Hier wurde mit COPY ein Wire aus einem NET-Segment kopiert, dadurch entsteht ein NET-Segment das keine durchgängige Verbindung mit dem Ursprünglichen NET-Segment besitzt.

COPY von NET-Wire sollten vermieden werden, man erspart sich nicht viel Arbeit im Gegensatz zum Zeichnen einer Netlinie mit dem NET-Befehl, da man entweder dieses Net-Segment mit NET verbinden muß, oder an allen beteiligten Net-Segmenten ein LABEL platzieren muß.

F

G

## ERC - Fehlermeldungen

A

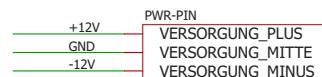

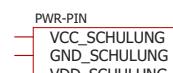

### - POWER-Pin Part-Name Pin-Name verbunden mit Netname

Ein PWR-Pin (Power Pin) ist der Versorgungsanschluss eines Bauteiles und wird in der Regel mit dem Namen des Netzes benannt, das dieses Bauteil mit der entspr. Spannung versorgt. Der Gedanke ist, dass man in der LBR schon festlegen kann/muß, mit welchem Netz/Spannung das Bauteil versorgt werden soll.

Wird an dem Pin ein Netz angeschlossen das nicht dem Namen des Pins entspricht, dann wird eine Warnung ausgegeben.

Damit wird versucht den Anwender bei der Suche nach Fehlerquellen in der Verdrahtung zu helfen. In der Praxis wird es jedoch immer wieder zu Kompromissen kommen, da man die Netze nicht immer so benennen kann, wie der Name der PWR-Pins.

Beispiel:

Im Datenblatt des einen Bauteil steht VCC, im Datenblatt eines anderen Bauteil steht +5V, in einem weiteren Datenblatt steht VDD. Im Symbol in der Bibliothek benennt man die Pins wie im Datenblatt, im benutzen Schaltplan soll den Netzname +UB lauten. Hier muß man einen Kompromiss eingehen und die Warnungen billigen (akzeptieren).

Eine etwas unpraktikable Möglichkeit wäre es, die Pins in der LBR so zu benennen wie den Versorgungs-Netznamen im aktuellen Schaltplan, nur wenn wegen einem andern Schaltplan die Pins in der LBR wieder anders benannt werden, und in einem weiteren Schaltplan ein UPDATE durchgeführt werden muß, dann ergeben sich durch den UPDATE beim nächsten ERC wieder die entsprechenden Fehler da die Pinnamen dann gleich dem aktuellen Stand der LBR sind.

Man merkt also, hier ist billiger die einfachere Möglichkeit.

B

### - Junction verbindet Netze Netname und Netname scheinbar

Hier wurde mit COPY ein Junction von einem anderen Netz auf diesen NET-Wire kopiert, wobei der ursprüngliche Netz-Name des Junction erhalten bleibt.

Eine weitere Fehlerquelle ist, wenn mit (Group) MOVE ein Junction auf ein Netz geschoben wird. Auch hier bleibt der ursprüngliche Netz-Name erhalten.

Merke: Niemals Junctions mit COPY oder MOVE auf eine anderes Netz bewegen, man spart sich keine Arbeit, da der Befehl JUNCTION nicht mehr Mausklicks benötigt als COPY oder MOVE.

C

### - Fehlende Junction in Netz Netzname

Bei elektrischen Abzweigungen/Kreuzungen sollte ein JUNCTION gesetzt sein, um sie von reinen optischen Kreuzungen von Leitungen zu unterscheiden.

Fehlende Junction entstehen, wenn unter Optionen - Einstellungen - Verschiedenes die Option [ ] Junction automatisch setzen nicht aktiv ist.

D

### - Nahe beieinander liegende, aber unverbundene Linien in Netz xxx

Hier wurde mit COPY oder MOVE ein Netwire dieses Netsegmentes zu einem Strang zusammen kopiert oder geschoben. Der Netz-Name ist zwar gültig, aber die Wire selbst gehören nicht zum gleichen Net-Segment.

E

### - Nahe beieinander liegende, aber unverbundene Linien in Netzen xxxx und xxxx

Werden mit COPY oder MOVE Netwire zu einem Strang zusammen kopiert oder geschoben bleibt der Netzname der Wire erhalten und wird nicht elektrisch mit den sich berührenden Wiresegmenten verbunden.

COPY und MOVE von unterschiedlichen Net-Wire-Segmenten auf andere Netwire bringen keinen Vorteil bezüglich der Arbeitsaufwand, da der Aufwand für MOVE und COPY der gleiche ist, wie direkt zeichnen.

Im Gegenteil, diesen Fehler zu beseitigen bedeutet mehr Mausklicks als direkt zu zeichnen.

F

### ACHTUNG :

Mit dieser Methode werden zwar optisch Verbindungen gezeichnet, aber im Layout gibt es dazu keine resultierende Luftlinie, also eine fehlende Verbindung die dann logischerweise auch nicht geroutet werden kann !

G

## ERC - Fehlermeldungen

A

- Pin an XXXX angeschlossen ohne Netz-Wire, Junction oder anderen Pin

! dieser Fehler muß noch gezeichnet werden !

B

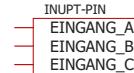

- Nicht angeschlossener INPUT-Pin Partname Pinname

Eine Ausnahme bilden Pins mit der Direction IN (Eingang). Diese Pins müssen immer mit einem Pin mit einer entsprechenden Direction wie OUT, PAS, IO oder SUP verbunden werden. Man geht davon aus, dass ein IN-Pin einen relativ hohen Eingangswiderstand und Empfindlichkeit besitzt, wie z.B. die Eingänge eines C-MOS Bauteil. Hochohmige Eingänge wie bei C-MOS Gattern driften zwischen der negativen und positiven Versorgungsspannung und verursachen dadurch ein Problem wenn die Spannung am Pin in den verbotenen Bereich kommt. Dadurch kommt es im IC zu unkontrollierten Schwingungen innerhalb der Chip, wodurch intern sehr hohe Ströme fließen können (Umladung der internen Kapazitäten) die wiederum eine extreme Wärmehyperentwicklung nach sich ziehen und den Chip zerstören. Es wird nicht unterschieden, bzw. es gibt keine Unterscheidung zwischen IN-Pins mit internen Pull-Up-Widerständen und ohne interner Beschaltung. Hier fehlen eigentlich weitere Direction-Typen.

C

- Kein SUPPLY-Pin für POWER-Pin Partname Pinname

Ein PWR-Pin definiert eine Versorgungsspannung für das Part (Bauteil), dazu muß es dann einen Supply-Pin irgendwo auf dem Schaltplan geben, der die Einspeisung repräsentiert.

In diesem Fall müßte je ein Device mit einem SUP-Pin angelegt werden, mit jeweils einem Pin-Namen

VCC\_SCHULUNG

GND\_SCHULUNG

VDD\_SCHULUNG

Beispiele siehe supply1.lbr

D

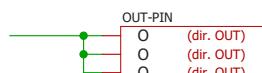

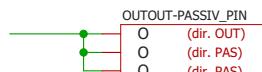

- Mehr als ein OUTPUT-Pin an Netz xx

Da ein OUTPUT-Pin in der Regel eine niederohmige Ausgangsspannung liefert, dürfen nie mehr als ein OUTPUT-Pin an einem Netz angeschlossen sein. Liefern die Out-Pins nicht exakt die gleiche Spannung, so fließt ein Strom von dem Ausgang mit höherem Spannungspiegel zu dem Ausgang mit niedrigerem Spannungspiegel, was zur Folge hat, dass wenn die Ausgänge nicht Kurzschlußfest sind, entsprechend hohe Ströme fließen können die das Bauteil zerstören.

Hat ein Bauteil mehrere OUT-Pins für den gleichen Ausgang, dann empfiehlt es sich nur einen PIN als OUT zu definieren und die anderen als PAS(siv). Dadurch kommt es zu keinem ERC-Fehler.

E

Die zweite Möglichkeit wäre die Fehler zu billigen, was aber den Nachteil hat das wenn das Symbol verschoben werden sollte, die Fehler wieder auftauchen, da für jeden Fehler ein Hash-Wert gespeichert wird in dem auch die Position (Koordinate) eingerechnet ist.

- Nur INPUT-Pins an Netz xxx

INPUT-Pins sollten mit einem Signal versorgt werden, da sie sonst keine Funktion haben. Unbenutzte TTL-Eingänge haben in der Regel zwar Pull-Up Widerstände, sollten aber trotzdem mit einem externen Widerstand nach + gezogen werden (siehe auch Datenblatt des Hersteller). Unbenutzte CMOS-Eingänge mit einem Widerstand nach GND gezogen werden um das schon beschriebene driften (floaten) zu verhindern.

G

## ERC - Fehlermeldungen

A

- Netzname XXX ist im Bus xxxxx nicht enthalten

Ein BUS hat den Vorteil, dass man mehrere Netze als Bündel durch den Plan ziehen kann, ohne jede Leitung mit viel Platzverbrauch zu verlegen. Mit dem NET-Befehl auf einen BUS geklickt, öffnet ein Menü in dem alle im BUS vorhandenen Netze ausgewählt, und vom BUS weg gezeichnet werden können.

Wird ein NETZ mit dem NET-Befehl von außerhalb dem BUS auf einen BUS-Wire gezeichnet, und der Name dieses NET ist nicht im BUS enthalten, wird das mit einer entsprechenden Meldung quittiert und der NET-Wire lässt sich nicht auf dem BUS absetzen.

Wird allerdings mit MOVE ein NET-Wire-Ende oder ein Stützpunkt (Knickpunkt) auf einen BUS gezogen, wird das von EAGLE nicht überprüft, ebenso wenn mit GROUP MOVE ... ein NET-Wire auf einem BUS-Wire landen würde.

Um diesen Fehler zu beheben kann man entweder den Namen dieses Netzes im BUS eintragen, oder das Netz vom BUS weg ziehen.

B

C

D

E

F

G

# Design-Rule-Check DRC

A

Die Design-Rules beschreiben die Regeln nach denen das Board geprüft wird.

Prüfen von Kupfer:

Dabei wird elektrisches Kupfer von nicht elektrischen Kupfer unterschieden. Elektrisches Kupfer ist alles Kupfer das an einem PAD oder SMD eines Bauteil über den SIGNAL-Namen angeschlossen ist.

Nicht-elektrisches Kupfer ist TEXT oder sonstige Linien, Kreise (CIRCLE), Rechtecke (RECT) und Polygone die einen Signalnamen haben der zu keinem echten Signal gehört, oder in einem Package z. B. als Logo definiert ist. \*

Für elektrisches Kupfer können Netz-CLASSen definiert werden, in denen die Clearance (Abstand zu Kupfer eines anderen Signal \*\*) und die Width (Kupferbreite für das Kupfer dieser CLASSEN) definiert ist.

Sind keine CLASSen definiert, bzw. sind die Werte in den CLASSen kleiner wie in den DRC-Einstellungen, dann wird alles mit den DRC-Einstellungen geprüft. Es macht also Sinn, sich entsprechende CLASSen zu definieren wie z. B. 'Versorgung', 'Mittelpotenzial', 'Hochspannung', 'Klein-Signale', 'Hochstrom' ...

Die CLASS 'default' gibt es immer, die für alles Kupfer zuständig ist, das zu keiner besonderen CLASS gehört.

Kommt im Layout Text vor, oder ist ein Logo mit einem Polygon definiert, so kann man im DRC-Menü die Clearance und Width entsprechend klein einstellen, so das nicht elektrische Objekte keinen Width (Breiten) Fehler und keinen Clearance (Abstands) Fehler erzeugen.

Für alles elektrische Kupfer müssen die Werte der CLASSen entsprechend eingehalten werden. Damit ist gewährleistet das elektrisches Kupfer auch zu nicht-elektrischen Kupfer die richtigen Abstände einhalten muß.

Restringbreite um PADs und VIAs.

In der LBR wird der Bohrdurchmesser für PADs angegeben, so wie der PAD-Aussendurchmesser definiert. Im Layout wird für VIAs der Bohrdurchmesser in den Netz-CLASSen bzw. in den Parametern der VIA selbst so wie der Aussendurchmesser angegeben.

In den Design-Rules kann man zusätzlich noch einen Wert für den Restring von PADs und VIAs angeben, der eigentlich dazu gedacht ist, dass man einerseits die Restringe nicht unterschreiten kann, andererseits bei Prototypen die man von Hand anfertigt (bohrt) größere Restringe bekommt.

Normalerweise stellt an den Wert für Restringbreite entweder auf 0, oder auf den kleinsten Wert der in den benutzten PADs vorkommt.

Vorsicht bei Feinstleiterstrukturen, werden hier Restringwerte eingestellt die einen größeren PAD ergeben als in der LBR definiert, kann es zu Kurzschlüssen kommen, bzw. zu Abstandsproblemen bezüglich der Spannung.

Deshalb im DRC-Menü in der Karteikarte Restring die Min. Werte immer auf 0 und vor allem die % Werte ebenfalls auf 0 stellen.

\* TEXT, CIRCLE und RECT können keinen Signalnamen erhalten.

WIRE und POLYGONE die im Board definiert sind erhalten immer einen Signalnamen, unterscheidet sich dieser Signal-Name von allen anderen Signal-Namen, die an mindestens einem PIN angeschlossen sind, dann handelt es sich um nicht\*\* elektrisches Kupfer.

\*\* Nicht elektrisches Kupfer wird wie Kupfer eines fremden Signal behandelt.

Polygone werden nicht geprüft, da sie mit den Design-Rule-Parametern und den CLASSen-Parametern berechnet werden. Bei Polygone ist zu beachten, dass der Parameter [ ] Orphans (verwaiste Flächen) entsprechend gesetzt ist. Verwaiste Flächen sind elektrisch nicht angebunden und können EMV-Technisch zu Problemen führen.

Zeigt der RATSNEST nach berechnen der Polygon eine oder mehrere Luftlinien für das entsprechende SIGNAL, dann kann das Polygon entsprechende Inselbereiche nicht durchgängig erreichen. Hier kann man dem Polygon auf die Sprünge helfen indem man per Hand in den entsprechenden Bereichen eine oder mehrere VIAs mit dem Signal-Namen setzt, vorausgesetzt auf einer der anderen Kupferlagen ist von diesem Signal eine angebundene Kupferfläche (Polygon).

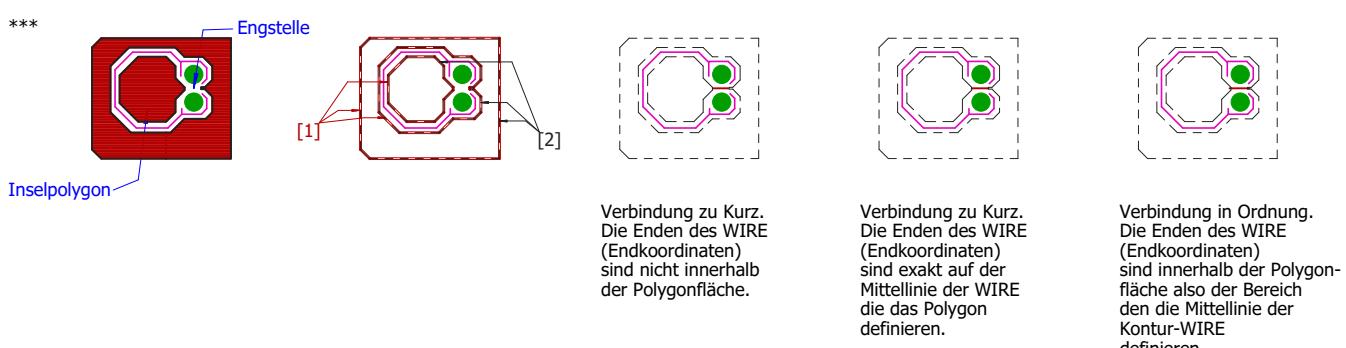

Oder man verlegt mit WIRE 'name' ein Stück Leiterbahn aus dem äusseren Bereich des Polygon in den inneren Bereich (Insel) des Polygon. Hier ist rarauf zu Achten dass die Enden des WIRE von den Polygonflächen angebunden werden können. \*\*\*

Die äusseren Ränder [1] der (berechneten) Flächen werden durch die endliche WIRE-Breite (Aussenkannte) [1] bestimmt, die Fläche zur Anbindung eines Objektes wird durch die Fläche innerhalb der Mittellinie [2] der Konturwire bestimmt.

Der Verbindungs-Wire muß mit den Endkoordinaten mindestens eine EAGLE-Einheit innerhalb der definierten Flächen liegen.

Eine EAGLE-Einheit == 3.125nm

PAD SMD an Polygone anbinden.

Polygone bzw. Inselflächen von Polygone werden nur am Zentrum eines PAD oder SMD oder an der Anfangs/End-Koordinate eines WIRE (Kette) die im Zentrum des PAD/SMD beginnt angebunden.

Man muss sich die berechnete Kontur des Polygon mit der halben Wirebreite vorstellen, also als wenn in der Mitte des Kontur-Wire eine Linie [2] gezogen wird, und nur die Zentrumskoordinaten von PAD/SMD und bei Singal-Wire ebenfalls diese gedachte Mittellinie müssen innerhalb der Fläche sein die dieses Linie umrandet. Alle anderen Objekte mit entsprechenden Koordinaten ausserhalb dieser Fläche werden vom Polygon nicht erreicht und erzeugen eine Luftlinie.

## DRC-Fehlermeldungen

A

Prüfen sonstiger Objekte wie:

Boardkontur, Bohrungen, Masken, Text

Die Boardkontur (Layer 20 Dimension) stellt die Aussengrenze der Platine dar. Sollte es innerhalb der Platine Ausbrüche geben, werden diese ebenfalls im Layer 20 Dimension gezeichnet. Hier stellt man die Wirebreite (Strichbreite) auf 0, dadurch gibt es keine Diskussion ob an der Innenkante der Linie, der Außenkante der Linie oder in der Mitte der Linie gefräst werden soll.

Die Strichbreite 0 hat auch den Vorteil, dass sie immer mit einer Einheit der maximalen Auflösung des Ausgabegerätes dargestellt wird, egal mit welchem Skalierungsfaktor (zoom) die Daten ausgegeben werden.

Holes erzeugen ebenfalls einen Kreis (Circle) mit der Strichbreite von 0 im Layer 20 Dimension, da sie wie ein Durchbruch ohne Kupfer zu sehen sind.

Der DRC-Wert Dimension ist der Wert den jedes Kupfer zur Kontur der Platine als Abstand einhalten muss.

Kupfer sollte nie bis zur Kante der Platine gehen, außer die Stirnseite der Platine soll verkupfert werden. Ist dies der Fall, dann sollte an der Boardkontur zusätzlich im Layer Milling eine Ausfräse angelegt werden und an der Stelle an der das Kupfer seitlich über den Rand gehen soll die Linie im Layer Dimension etwas nach außen verschoben werden, so das der Dimension-Parameter eventuelle Kupferpolygone und Wire nicht als Fehler meldet.

Bohrungen werden auf deren Abstand entsprechend der Einstellungen im DRC-Menü Distance geprüft. Hier wird der Rand der Bohrung zum Rand der nächsten Bohrung überprüft. Bohrungen die leicht versetzt sind so das die zweite Bohrung nur zum Teil in die erste Bohrung hineinragt, machen beim Bohren selbst ein Problem, da bei der zweiten Bohrung der Bohrer sich das Loch der ersten Bohrung abdrifft, zu wenig abzutragendes Material auf dieser Seite, worauf der Bohrer so stark abgelenkt wird dass er abbricht.

Die Lötstopmaske (Stop-Mask). Hier kann in den Design-Rules und Mask ebenfalls ein Übermaß angegeben werden, und auch hier ist in der Regel der Wert auf 0 gestellt, da sonst bei feinem Grid von SMDs die Maske so weit vergrößert werden kann, dass zwischen den SMD-Lötflächen kein Lötstopplack mehr gedrückt wird so dass beim Löten das Zinn dann zwischen den SMDs fließen kann. Achtung Kurzschlußgefahr.

Die Prüfung von Lötstop-Masken bezogen auf den Bestückungsdruck ist nur relevant wenn ein Bestückungsdruck vorgesehen ist.

Die Cram-Maske (Lötastenmaske) wird in der Regel in der Bibliothek im Package des Bauteil vorgegeben, hier kann im Board ebenfalls in den Designrules ein Untermaß vorgegeben werden, auf das die Cream-Maske dann vom DRC entsprechend erweitert (in diesem Fall verkleinert) wird.

Das ist jedoch mit Vorsicht zu genießen, zumindest bei Finepitch-Bauteilen.

Bei beiden Parametern sollte der Wert für Min. und für % auf 0 gesetzt werden.

Text im Kupfer ist nichtelektrisches Kupfer und wird nur mit den Width- und Clearance-Parametern der Design-Rules geprüft. Die CLASS-Parameter haben hier keine Bedeutung, weshalb man Texte entsprechend klein machen kann, selbst auf die Gefahr hin, dass sie nicht ätzbar sind, was bedeutet, dass sie nach dem Ätzprozess eventuell teilweise oder ganz verschwunden sind. Je nach Leiterplattenhersteller und der Kontrolle über den Ätzvorgang kann das Ergebnis unterschiedlich ausfallen. Soll der Text auf jeden Fall erhalten und lesbar sein, empfiehlt es sich beim Leiterplattenhersteller nachzufragen wie fein die Strukturen für Texte sein dürfen.

Hinweis:

Es wird nur auf die Einhaltung der Mindestbreite geprüft, wenn also das Kupfer wesentlich breiter ist als in der CLASSen bzw. Design-Rules, dann erfolgt keine Meldung, denn breiter ist auch niedriger.

Ebenso bei den Abständen (Clearance), je größer um so weniger das Übersprechen von Leitung zu Leitung bzw. Spannungsüberschlag.

C

D

Die DRC-Fehlermeldungen können mit `RUN export-error.ulp` auch in eine externe Datei zur Dokumentation gespeichert werden.

Innerhalb des ULP werden die Fehlermeldungen teilweise noch weiter erklärt.

E

F

G

A

\*[1]

Das automatische setzen eines Junction kann mit den SET-Optionen ein und ausgeschaltet werden.

Optionen

- Einstellungen

- - Verschiedenes

Junctions automatisch setzen

Oder mit dem SET-Befehl:

SET AUTO\_JUNCTION OFF | ON;

Siehe auch HELP SET ...

B

C

D

E

F

G

A

B

C

D

E

F

G

**Vorläufiges Ende der Dokumentation 2020-09-21

EAGLE-Schulung\_DRC-ERC

A. Zaffran**