Aufheben der Bergrenzung der FREEWARE / STANDARD-Edition.

Die Begrenzungen im Schaltplan:

Man kann nur 2 Schaltplanseiten anlegen mit je ‡2m, (also 4 x 4m). Das sollte für private Zwecke ausreichen, allerdings steht dann nur eine MODUL-Seite zur Verfügung.

Hier kann man aber die komplette Fläche von 4 x 4 m zum Platzieren von Symbolen nutzen. Beim Ausdruck des Schaltplan gibt es allerdings einen (zwei) kleine(n) Wermutstropfen.

Falls die Schaltplanseite größer als die Papiergröße des zur Verfügung stehenden Drucker ist, druckt EAGLE den Schaltplan auf mehrere Seiten verteilt.

Hier ist der Übergang zwischen den Seiten Pixel genau, so dass man an zwei Seiten des Papier den Rand wegschneidet und die Seiten zusammenklebt. Was aber bei 4 x 4m nicht

unbedingt Spaß macht.

Man kann aber auch Zeichnungsrahmen mit entsprechenden Abstand* auf der Seite platzieren und dann entsprechend die Papiergröße und den Rand beim Drucker wählen.

Damit erhält man auch eine saubere Dokumentation. Allerdings funktionieren die XREF-Label innerhalb einer Seite nicht. Ebenso die Seitennummerierung der einzelnen Seiten.

Bei 2 Seiten ohne MODUL kann man sogar die XREF-Label nutzen, aber wie gesagt, nicht innerhalb der gleichen Seite.

Sollten aus welchen Gründen auch immer, für den Schaltplan die 4 x 4m nicht reichen, dann kann man sich die Symbole in den Bibliotheken entsprechend Runter skalieren.

Aber Vorsicht: Die Pin-Länge (Length) kann nicht beeinflusst werden. Es gibt 4 fest vorgegebene Längen:

- Point | Ist ohne dem grünen Kreis im Layer Pins nicht sichtbar. (DISPLAY 93)

- Short | Eine Linie mit Breite 6mil und einer Länge von 100mil dem kürzesten sichtbaren PIN

- Middle | Eine Linie mit Breite 6mil und einer Länge von 200mil des sichtbaren PIN

- Long | Eine Linie mit Breite 6mil und einer Länge von 300mil der längste sichtbare PIN

Beim Runter skalieren eines Symbol muß deshalb jeder PIN zu Point geändert werden und die angezeigte Pinlänge mit WIRE im Skalierungsmaßstab

nachgezeichnet werden. Ebenso müssen die PIN- und PAD-Namen als TEXT mit der entsprechenden Skalierung positioniert werden.

Einen kleinen Nachteil hat diese Methode. Bei SHOW wird i.d.R. die sichtbare PIN-Linie so wie PIN- und PAD-Name

mit entsprechender Farbe gehighlighted, das funktioniert jetzt nicht mehr, da die Linie und die Texte nicht mehr zu dem Objekt PIN gehören.

Möchte man bei mehreren Seiten mit einem Zeichnungsrahmen auch eine Nummerierung der einzelnen Seiten, dann kann man sich hier mit einem ULP behelfen.

Weitere Infos zu ULP gibt es hier .

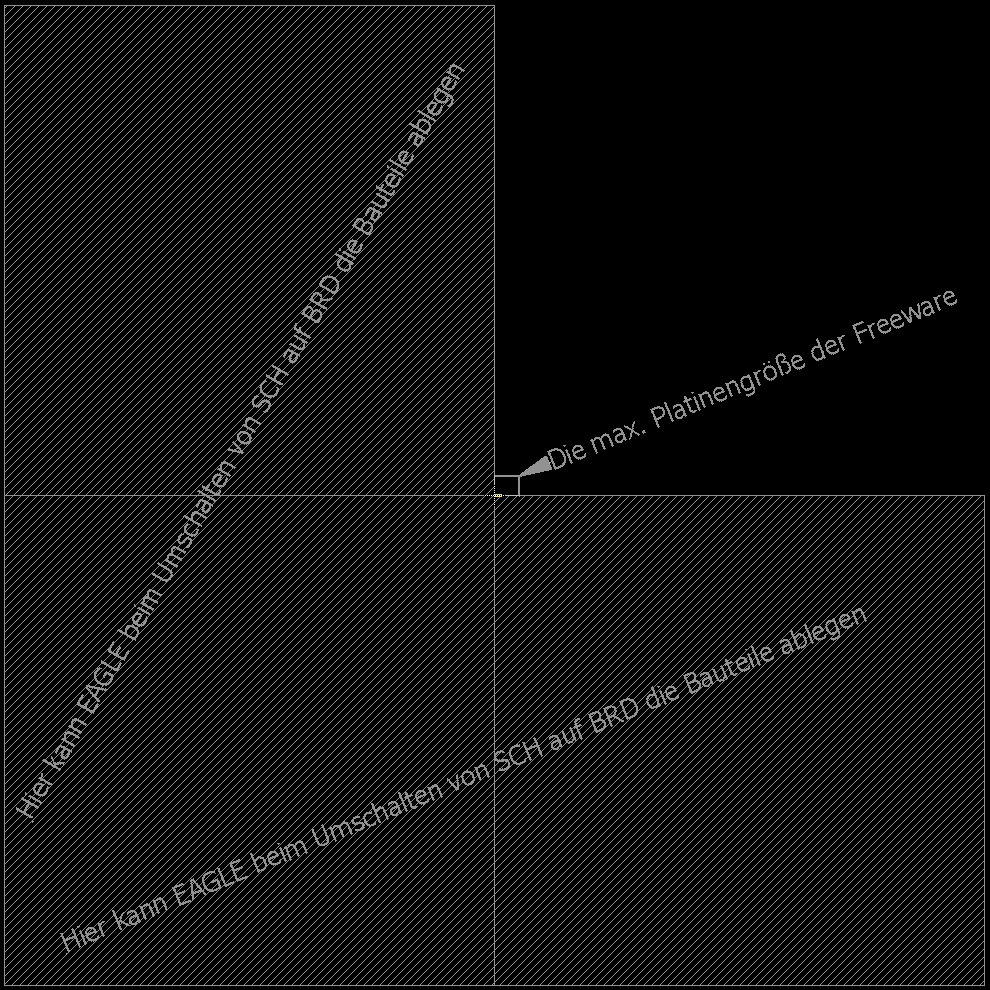

Die Begrenzungen im BOARD:

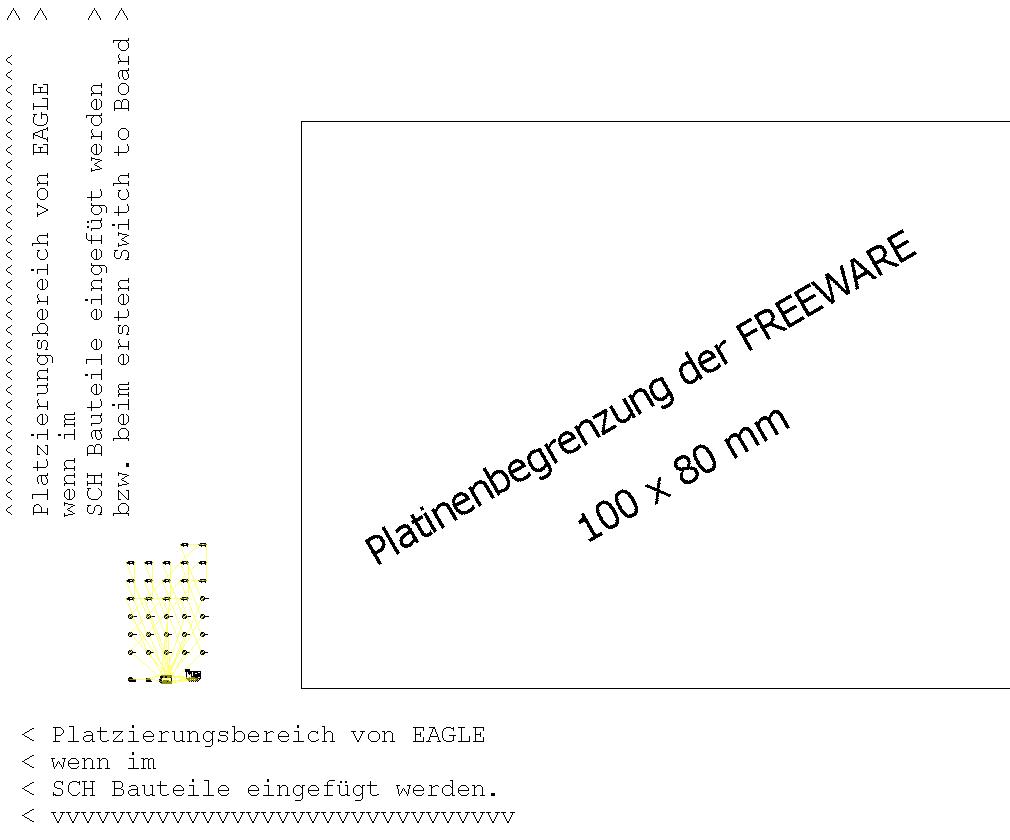

Im BOARD hat EAGLE in der Freeware eine Bergrenzung auf 100x80mm und 2 Kupferlagen.

Die Standard-Edition auf 160x100mm und 4 Kupferlagen.

Was aber nicht bedeutet dass man keine größeren Platinen machen könnte.

Die Absolute Grenze ist ±2m, also insgesamt 4m in X und Y.

<< Maus

<< Maus

Die Begrenzung bezieht sich eigentlich nur auf die Platzierung von Bauteilen mit elektrischen Kontakten, also PAD und SMD.

Das Bedeutet, man kann keine Packages im Bereich -X -Y und größer X +100mm und Y +80mm platzieren, wenn einer der Kontakte außerhalb dieser Koordinaten zu liegen kommen würde.

In der Standard-Edition man kann keine Packages im Bereich -X -Y und größer X +160mm und Y +100mm (Europakarte) platzieren.

Versucht man es trozdem, gibt EAGLE eine Fehlermldung aus Einige Objekte stehen über die erlaubte Boardfläche hinaus.

Das ist aber kein Problem, da man die Zeichnungen im Maßstab 1:10 * (oder 1:100) anlegen kann, da die interne Auflösung von EAGLE 3.125nm ist, reicht diese Genauigkeit.

Wem also die Platinengröße von 100x80mm zu klein ist, der kann einfach die Bauteile (Packages) in den Bibliotheken entsprechend Runter skalieren (dazu gibt es ein kleines ULP cmd-scale-xy-pac-sym.ulp).

Dann müssen nur die Design-Regeln (DRC) bezüglich der Leiterbahnbreiten, Abstände, Bohrungen und Restringe von PAD und VIA entsprechend um den gleichen Faktor angepasst werden,

und schon kann man Platinen mit * 1000x800mm erstellen.

Wichtig ist dann nur, dass bei der CAM-Ausgabe der Faktor 10:1 eingestellt werden muss und man dem Leiterplattenhersteller die Gerber- und Excellon- (Bohrdaten) Daten sendet.

Würde man dem LP-Hersteller die Ealge-BRD-Datei senden, dann würde man eine Plaine um den Faktor 10 zu klein erhalten.

Ein Besonderheit ist die Platzierung der Packages von EAGLE selbst.

Schaltet man zum ersten mal vom Schaltplan zum Board um, platziert EAGLE die Packages links von der Koordinate X 0.0 und auch oberhalb wie unterhalb der Koordinate Y 0.0. Also im verbotenen Bereich.

<< Maus

<< Maus

Irgendwo muß EAGLE ja die Packages zuerst mal ablegen ohne dass sie im Weg sind.

Fasst man jetzt ein Package mit MOVE (MIRROR, ROTATE) an, kann man es nicht mehr außerhalb der gültigen Bereich ablegen. Das ist nur EAGLE selbst vorbehalten!

Die wichtigten Grundeinstellungen für den Grenzenlosfaktor

Jetzt noch die Einstellungen für den DRC, CLASS, ROUTE und Anzeigegröße von Referenz-Bohrsymbolen.

| Optionen | Einstellungen | Verschiedenes [x] Width und Drill bei Route autom. setzen. | Der ROUTE-Befehl holt sich aus den CLASS-Einstellungen des aktuellen SIGNAL die WIRE-Breite |

| Optionen | Einstellungen | Bohrsymbole | Symbole -- Durchmesser [ ] -- Strichstärke [ ]. | Wie groß das Refenzsymbol für die Drills und Holes angezeigt werden soll |

Mal so ganz nebenei, hier ein Beispiel für ein Projekt das ich extra mit der Freeware erstellt habe. ;-)

Bauteile platzieren, eine Wissenschaft für sich

Jetzt ist der Layouter gefragt, denn nur Er kann wissen wo Befestigungsbohrungen, Steckverbinder und alle übrigen Bauteile platziert werden müssen.Manche Anwender fragen auch nach einem Auto-Placer, nur woher soll der wissen wo die Bauteile hin müssen?

In manchen CAD-Systemen gibt es so einige mehr schlechte als rechte Versuche einen Autoplacer zu integieren, aber geschafft hat das noch keiner.

Auch für den EAGLE haben Anwender mal versucht mit einem ULP einen Autoplacer zu realisieren, das ging aber voll in die Hose.

Weil wie oben schon angesprochen, woher soll der Autoplacer wissen wo Befestigungsbohrungen und Steckverbinder platziert werden müssen.

Das sind bezogen auf die Platzierung die wichtigsten Vorgaben, denn die müssen ja zu den Bohrungen und Durchbrüche des Gehäuse passen!

Nicht mal die Boardkontur ist zu diesem Zeitpunkt vorgegeben. Die kann auch nur der Anwender wissen, denn nur Er weiß in welches Gehäuse die Platine kommt.

Klar, man kann sich Packages mit der Kontur im Layer Dimension anlegen, vor allem dann wenn man immer wieder die gleiche Kontur für Platinen benötigt.

Ein Beispiel ist die Kontur für einer Platine in ein Unterputzgehäuse. ;-)

Aber dann weiß der Autoplacer immer noch nicht wo die besagten Bauteile platziert werden sollen.

Ein Ansatz eines ULP war, die Packages bezogen auf die Platzierung im Schaltplan vorzunehmen, aber des klappt auch nicht wirklich. Ok, man nimmt einen IC und platziert die anderen Bauteile drum herum,

wie in Schaltplan. Nur was macht man wenn ein IC aus mehreren Gates besteht und die auf verschiedenen Seiten platziert sind. Beispiel 4-fach NAND. Jedes Gate kann auf einer anderen Schaltplanseite sein,

und dann noch Verbindungen mit NETzen über ein NET-Label realisieren. Da ist jeder Algorithmus schnell am Ende. Und selbst **KI kommt hier nicht weiter.

Dazu kommt auch noch die Berücksichtigung von Leiterbahnführungen bez. Leiterbreite (Stromstärke), Spannungsabstände, Störeinflüsse wie induktive und kapazitive Kopplungen (Übersprechen).

Und die Überschattung der Bauteile bez. des Handling von Bestückungsautomaten muss auch noch berücksichtigt werden.

Man sieht also, da muss echte Intelligenz her.

**KI ist nicht wirklich eine Intelligenz. Tatsächlich sind das nur Datenbanken die man antrainieren kann, und sie sind nur so gut wie die Trainingsvorlagen.

Apropos KI und ChatGPT. Ich habe mir mal den Spaß gemacht und ChatGPT gebeten mir ein kleines ULP für EAGLE zu schreiben.

Selten so einen Murks von C-Code gesehen! Zwar hat ChatGPT irgendwoher erkannt das ein ULP in C geschrieben wird, aber mit den Dialog-Funktionen und den

speziellen Beschränkungen der integrierten C-Funktionen so wie Variablen-Typen der ULP-Sprache, kann diese "KI" nicht umgehen.

Da fehlt noch jede Menge Training!